發布日期:2022-10-18 點擊率:51

本文回顧了Serdes的發展歷程,提出了Serdes技術分代及其特點,講述當前國內外Serdes的技術現狀,以及Serdes技術的發展趨勢,對Serdes架構和各模塊技術演變、關鍵技術挑戰進行了分析,并從協議、電路設計、信號完整性、發展趨勢幾個維度加以詳細討論。

Serdes是英文單詞串行器(Serializer)和解串行器(De-Serializer)的合成詞,可以稱之為串行解串器。根據其功能來講,Serdes就是在發送端將并行數據轉換為串行數據,在接收端將串行數據恢復為并行數據的電路。

目前,Serdes技術在有線通信方面已經得到了廣泛應用。按照應用連接的類型,主要分為芯片與光模塊的互聯;芯片與芯片的互聯;以及以太網互連。

以太網接口主要有10BASE-T、10BASE-F、100BASE-T、10BASE-FX、1000BASE-X、1000BASE-T接口,在跨城市互聯中將主要用到GE及以上的接口。GE物理接口有1000BASE-X(802.3z標準)和1000BASE-T(802.3ab標準)兩種。未來的高速率接口(100G或以上)均為GE類型,為了與100GE兼容,OTU4標準的制定為100GE,高端路由器廠家目前均可提供100GE,并大部分計劃開發100GE OTN接口 。可以預見的是未來的高速端口將是以太網和OTN這兩種類型。

在以并行通信主導的內存顆粒的訪問接口領域,也有分別是海力士和AMD主導的HBM(High BandwidthMemory,高帶寬存儲器)以及Intel支持、美光主導的HMC(Hybrid Memory Cube)等串行接口,作為與DDR5不同的一種演進方向。

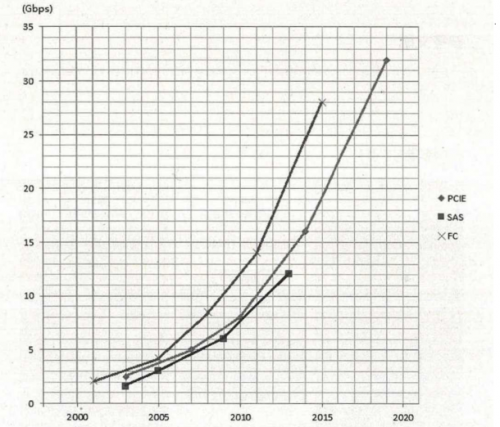

由此我們可以看到,Serdes已經跟隨通信協議,廣泛應用在電信、IT和個人消費電子領域。并且隨著通信容量的快速提升,各種通信協議的單通道數據率也快速提升,例如圖1所示的幾種協議演進。

圖1:部分協議的單通道數據率

1 技術現狀

目前,國際上最先進的Serdes單通道為64~128 Gbit/s之間。在功耗方面,除了單通道最大功耗(mW)外,由于電路功耗跟工作的數據率強相關,所以通常也使用每bit消耗的功耗(pJ/b)來衡量。在ISSCC 2019會議上,IBM發表的單通道128 Gbit/s 1.3 pJ/b的發送器和100 Gbit/s 1.1 pJ/b的接收器,基本代表了當前國際Serdes技術的最高水平 。

令人注意的是,華為旗下的海思半導體在Serdes領域也有相當先進的技術,已經形成了從45 nm~7 nm工藝,10 Gbit/s~64 Gbit/s的多款IP核,并在近百款芯片中商用。在2018年和2019年的ISSCC會議上,華為加拿大研究所先后發表了基于臺積電16 nm 64 Gbit/s和7 nm 60 Gbit/s的Serdes,并且接近商用,代表著國產Serdes技術的最高水平 。

另外,清華大學、北京大學、東南大學等院校在Serdes領域研究也取得了很大的進步,有多篇32Gbit/s、40Gbit/s、50Gbit/s的學術成果 。

2 發展歷程

Serdes技術的發展,依本文作者觀點,可以分為以下幾個階段。

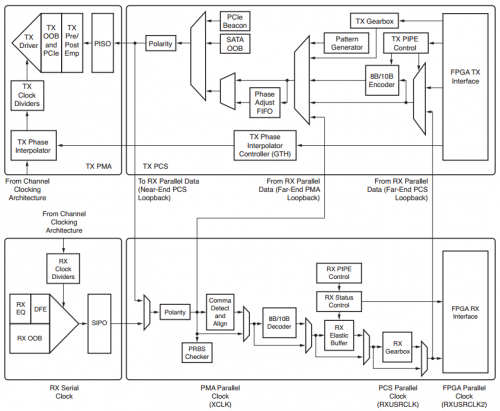

一個完整的Serdes系統,包括參考時鐘,PLL,上層協議,編解碼,發送端(Transmitter,TX),信道,接收端(RX)等部分組成。其中有源器件主要是芯片本身如Serdes的收發端,外部的ESD防護器件,光模塊等;無源器件包括單板、背板及走線,AC耦合電容連接器,背板,SMA頭,線纜等。

下面,我們進一步從這些方面討論Serdes的發展趨勢和挑戰。

3 協議

Serdes通常作為通信協議的物理層的物理介質(PMA)子層部分,由此要嚴格準從協議規定。Serdes作為一個芯片的底層模塊,除了滿足單一的通信協議數據率越來越高的挑戰,基于成本等考慮,通常還要求同一個Serdes IP核能夠兼容多種協議。

從Serdes設計的角度,常見的通信協議可以分為幾大類別。

4 鎖相環

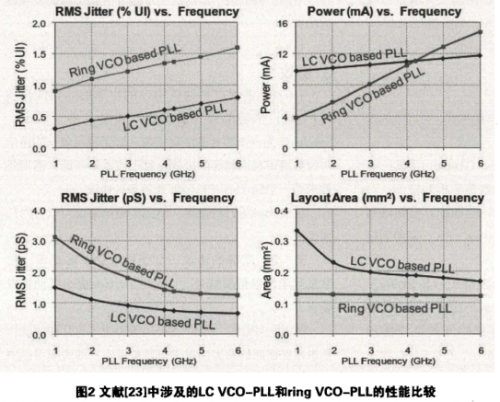

常見的鎖相環通常基于LC振蕩器(LC VCO)或者環形振蕩器(Ring VCO)結構。

環形振蕩器易集成、面積小、且容易產生多相位的時鐘。LC振蕩器的電感占用芯片面積較大,設計難度較高,優點是相噪性能更好。但是隨著Serdes數據率的提高,電感越小諧振頻率越高,所以電感占用面積大的缺點有所緩解。反而是環形振蕩器PLL的功耗、相噪等問題,無法滿足更高的要求。但是隨著Serdes對PLL頻率、相噪、功耗等提出了越來越高的要求。在10 Gbps以上的Serdes設計中,通常會使用基于LC VCO的PLL,以獲得更好的相噪水平。

從LC VCO-PLL和ring VCO-PLL的性能比較我們可以看出:LC VCO-PLL在抖動方面具有較大優勢,在約(4~5)GHz以下的低頻應用時,ring VCO-PLL在功耗和面積上有一定優勢。但隨著頻率的更加,ringVCO需要更大的電流來提高振蕩頻率,LC VCO占最大面積的電感和電容器件將更小,所以功耗和面積缺點不再那么突出了。

一般來說,在5~8 GHz以下的應用中,基于ringVCO的PLL是可行的。如果在更高的頻率,基于LCVCO的PLL更為合適。

5 發送端

發送端主要功能包括如下。

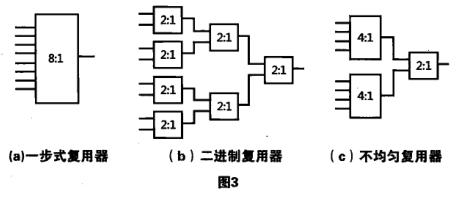

串行器的核心是多路復用器電路,常見的有3類:一步式的多路復用器,二進制的多路復用器,多種復用器組合不均勻串行器,如圖3所示。

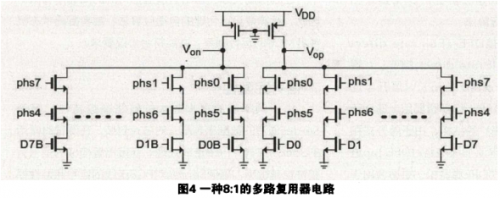

一種8:1的多路復用器如圖4所示。Phs0~Phs7是同頻率但等相位差的時鐘,只有在Phs7和Phs4同時為高時,數據D7B和D7才能被送出;只有在Phs0和Phs5同時為高時,數據D0B和D0才能被送出,依次類推。

循環的等相位差時鐘,將數據D0~D7和D0B ~D7B依次串行高速輸出,即可達到并行轉串行的目的。此類結構優點在于電路簡單,缺點是難以應用在數據位寬較寬的場景。而且在高速并串轉換時,對時鐘相位的抖動等要求很高,而變得難以實現。也就是說,一步式復用器的最高工作速率低于二進制復用器,所以一步式復用器一般應用在低速Serdes并串轉換電路中,或者作為不均勻串行器的第1級。

不均勻復用器,既可以靈活配置位寬,也避免了一步式復用器對多相時鐘的高指標要求,并且比二級制復用器更高效,因此是一種很適合高速串行器的結構。

發送端的驅動端電路,常見的是CML和SST結構。

CML結構本身方便電流疊加,所以很容易實現預加重功能。但是輸出擺幅與輸出阻抗和驅動電流的乘積相關,輸出阻抗通常又被限制在50~100 Ω,因此要獲得大擺幅就必須使用較大的驅動電流,使得功耗居高不下。這在功耗問題日益突出的今天,已經變得無法接受。

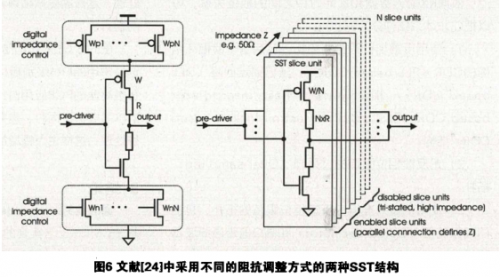

文獻中的兩種不同阻抗調整方式的SST結構如圖所示,SST結構的輸出擺幅與其電源電壓直接相關,一般來說產生同樣擺幅,SST結構的功耗只有CML結構的1/4左右,因此在10 Gbps以上的Serdes中越來越受到青睞。

但是SST結構的預加重信號疊加相比CML結構更為復雜。使問題更加困難的是,采用并聯SST等結構來實現預加重功能時,由于開關的MOS管數量不同,阻抗匹配難以保證。因此,通常需要阻抗校準電路和狀態機來保證初始化時,Serdes 發送端的阻抗能夠匹配在差分100 Ω左右。

6 接收端

信道的插損與信號頻率成正比,頻率越高衰減越大。所以隨著Serdes數據率提升,信道的衰減也越來越嚴重。為了補償信道的衰減,通常需要在發送端預加重功能和接收端均衡功能。接收端的均衡器一般由CTLE和DFE構成。CTLE和DFE已經廣泛應用于當前的Serdes架構中。

RX設計面臨的幾個挑戰是:更優的DFE拓撲和CDR拓撲,以及更優的自適應算法。

DFE架構經歷了全速直接DFE(Full rate directDFE)、半速直接DFE(Half rate direct DFE)、展開全速DFE(Full rate unrolled DFE)、展開半速DFE(Unrolled half rate DFE)和多路復用半速DFE(Multiplexed half rateDFE)等結構。由于展開式和多路復用等結構,不用通過電流加法電路對DFE tap進行求和,而使得時序比直接式DFE更寬松,更適合用于解決速率提升帶來的時序緊張問題。

根據RX輸入數據和本地時鐘之間的相位關系,可以把CDR體系結構分為3類。

也可根據應用場景將CDR分為突發模式和連續模式的CDR。突發模式系統通常用于點對多點應用中,不同的發送方在突發之間傳輸具有靜默時間間隔的包數據。

每當請求傳輸數據包時,數據傳輸鏈路被重新激活,并且在其他時間保持不活動狀態,如以太網無源光網絡(EPON)、千兆無源光網絡(GPON)等。突發模式CDR結構一般采用無反饋相位跟蹤的拓撲結構,如門控振蕩器和過采樣技術。基于相位插值器的CDR不存在抖動峰值或穩定性問題,具有無限的相位捕獲范圍,但存在量化誤差。

因此,需要根據芯片不同的應用場景來選擇最佳的Serdes CDR結構。

自適應算法可以由數字邏輯狀態機來執行,也可以固件的形式燒錄在片上MCU中執行。例如PCIE等協議在速率切換時,要求24 ms以內達到規定的誤碼率以下,否則協商失敗,留給自適應執行的時間非常有限。

因此,就需要設計合理的自適應算法,或者提高狀態機或者MCU的運行頻率,才能符合協議要求。

7 信號完整性

由于頻率越高插損越大的鏈路參數特性,隨著Serdes通道的數據率越高,對芯片封裝、在測試時常用的Socket夾具、PCB走線處理、連接器等構成的信號完整性也越敏感。高速Serdes對PCB走線的信號完整性提出了越來越嚴苛的要求,例如PCB板材的選取,過孔的處理,是否需要背鉆等等,都是信號完整性所要考慮的問題。

在5~8 Gbit/s以下的Serdes單板PCB設計時,一般選擇常用的FR4級別板材就能滿足信號完整性的要求;在更高速的PCB應用時,則要考慮M4、M6或者同級別的PCB板材。同時,需要對過孔進行埋孔、背鉆等做特殊處理,這樣也大幅增加了投板成本。

8 結論

通信業務對于Serdes數據率的需求日益增長,當前基于CMOS工藝實現的Serdes最高單通道數據率已經達到128 bit/s,無論對于CMOS電路設計還是鏈路信號完整性,單通道數據率的進一步提高已經變得越來越困難。與此同時,很多系統應用對Serdes的功耗的還有苛刻的要求,也是設計人員面臨的巨大挑戰之一。

硅光子技術可以基于硅和硅襯底材料,利用CMOS制程將電信號轉換為光信號傳輸。光替代鏈路的銅線,可以得到很好的傳輸數據率和極低的損耗。如果硅光子技術獲得突破和成熟,加上單板的光走線,可以實現芯片與芯片之間的光互聯,那么,Serdes技術的側重點會變得很大的不同,將對驅動能力要求大大的降低。因此,硅光子技術是一種極具可能性的演進方向 。(參考文獻略)

來源:電子產品世界

下一篇: PLC、DCS、FCS三大控

上一篇: 小基站助力5G連接