前些天我在博客上分享了使用FPGA+AD9361進(jìn)行DPSK調(diào)制的過程,相對(duì)于DPSK解調(diào)來說,DPSK調(diào)制過程比較簡單。一個(gè)顯而易見的問題是,作為發(fā)送端的AD9361與作為接收端的AD9361的本振頻率必定存在偏差,使得AD9361接收到的基帶數(shù)據(jù)像是被調(diào)制了一樣。我在嘗試分析本振頻偏問題時(shí),曾經(jīng)使用信號(hào)源生成DPSK信號(hào)并由AD9361接收,故意將信號(hào)源的本振頻率設(shè)定一點(diǎn)偏移,就可以發(fā)現(xiàn)AD9361接收到數(shù)據(jù)包絡(luò)跟著變化,因此,如果想正確解調(diào)DPSK數(shù)據(jù),就必須消除載波頻偏。

事實(shí)上,接收端解調(diào)時(shí)如果殘留頻偏(或者相位偏差)較大時(shí),系統(tǒng)的誤碼特性將出現(xiàn)平頂效應(yīng),此時(shí)無論信噪比增大多少,都不能使誤碼率顯著降低。受到一篇論文的啟發(fā),我采用了一種特別簡單有效的方法實(shí)現(xiàn)了DPSK解調(diào)的同時(shí),消除了載波頻偏,在此分享給各位讀者。

原理分析

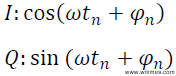

由AD9361接收,正交解調(diào)并AD采用后的n時(shí)刻基帶數(shù)據(jù)可表示為

n-1時(shí)刻基帶數(shù)據(jù)可表示為

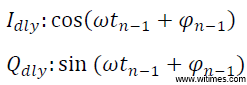

其中w是接收端與發(fā)射端的載波頻率偏差,利用三角函數(shù)公式,有

其中

通常,wTs近似為0,所以這個(gè)運(yùn)算得到的結(jié)果就是解調(diào)后的數(shù)據(jù)。

Matlab驗(yàn)證

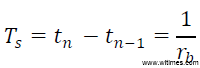

首先使用Vivado的ila抓取AD9361 AD采樣后的基帶數(shù)據(jù),如下圖,從圖中可以看出本來應(yīng)該是恒包絡(luò)的波形由于載波頻偏的存在嚴(yán)重變形了,就像被AM調(diào)制了一樣。

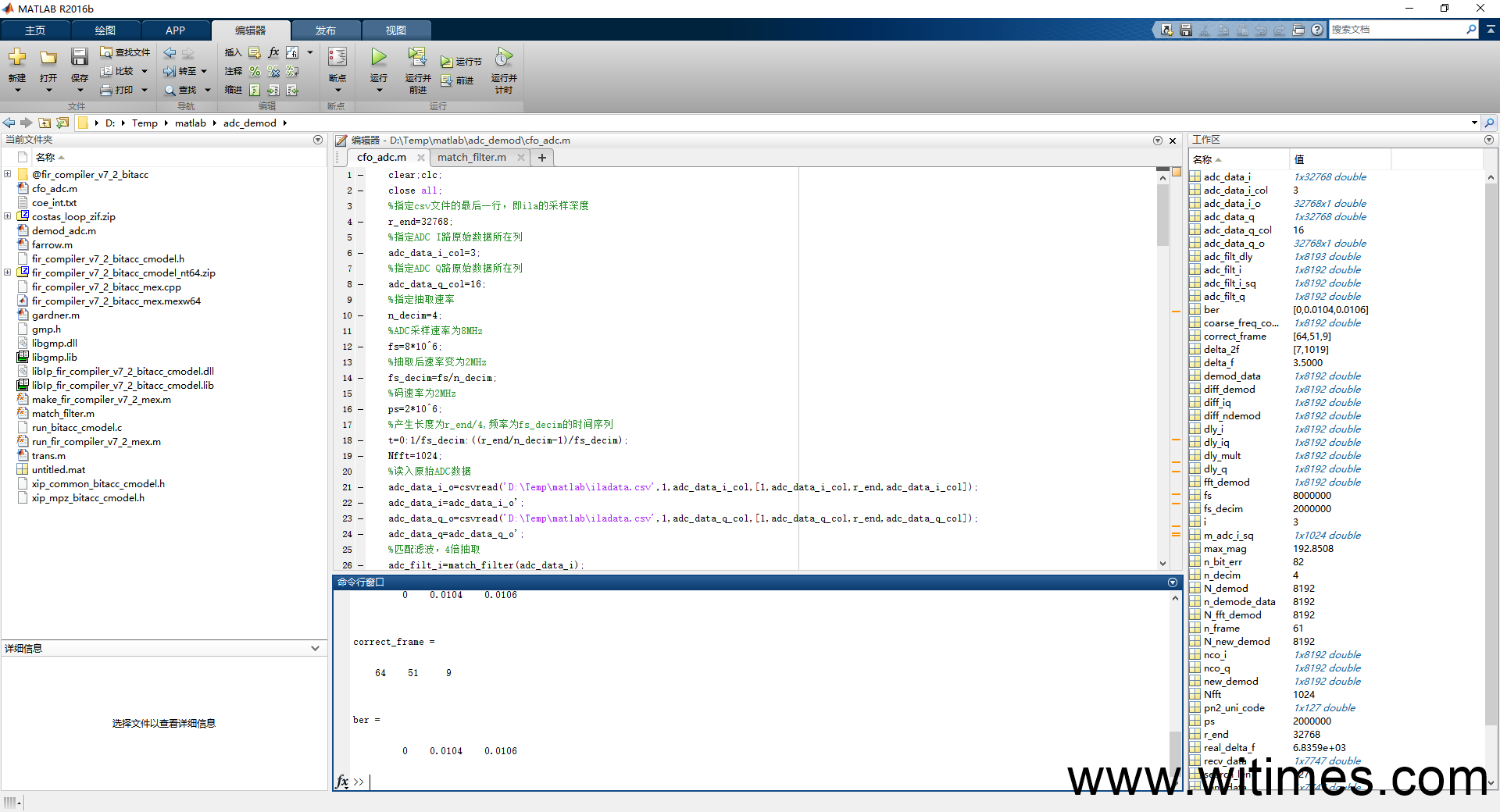

然后將ila抓取到的數(shù)據(jù)保存為csv格式,供Matlab使用。

在Matlab中將csv數(shù)據(jù)讀入,匹配濾波,抽取之后進(jìn)行頻偏補(bǔ)償,解調(diào),我采用了三種方式:

- 改進(jìn)型,即前文分析的方法

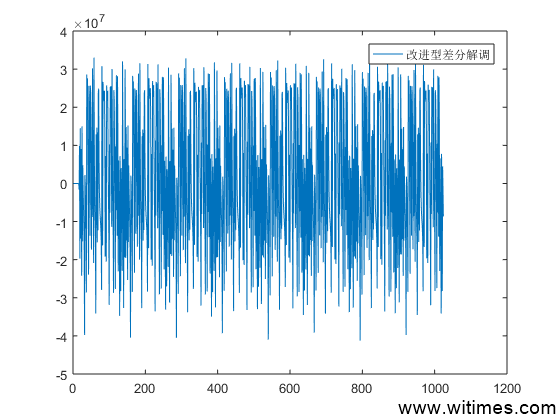

- FFT頻偏補(bǔ)償,對(duì)接收到的I路或者Q路基帶信號(hào)進(jìn)行FFT變換,得到載波頻偏,再將其與原始I路、Q路基帶數(shù)據(jù)相乘,相加,這種方式可以消除較大的頻偏,如多普勒頻移,但是會(huì)有殘留的頻偏及相偏,需要進(jìn)一步使用Costas環(huán)糾正

- 無補(bǔ)償

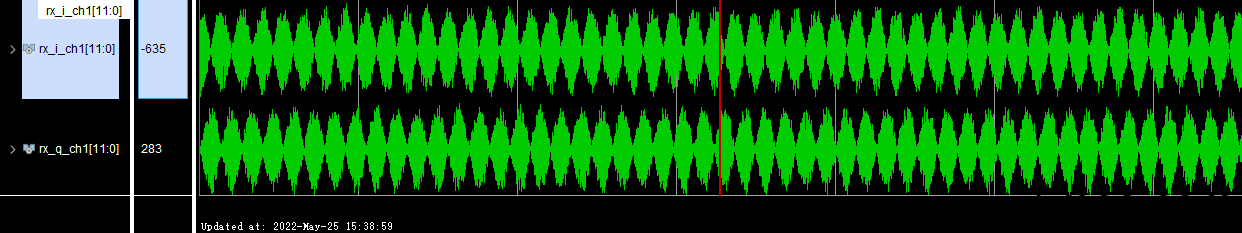

對(duì)于同樣的基帶數(shù)據(jù),三種解調(diào)方式得到的波形分別如下:

改進(jìn)型,可以看出載波頻偏已消除

FFT頻頻補(bǔ)償,可以看到仍有殘留的頻偏

無補(bǔ)償,可以看出這種情況最糟糕

在本例中,發(fā)送序列是已知的,所以可以輕易地構(gòu)造出較長的發(fā)送序列并與解調(diào)后的數(shù)據(jù)做對(duì)比,得到誤碼率,其結(jié)果如下,可以看出,改進(jìn)型DPSK解調(diào)的誤碼率為0。