在增加3D NAND層時(shí),最大的難題就是要克服芯片生產(chǎn)流程中對(duì)長(zhǎng)寬比的限制,否則層數(shù)將始終無(wú)法取得突破。串堆疊技術(shù)則能夠幫助我們有效解決這一長(zhǎng)寬比難題。

美光NAND晶圓

三星公司已經(jīng)開(kāi)始發(fā)布48層3D NAND,也就是其第三代產(chǎn)品;其相當(dāng)于把48塊平面(2D)NAND晶片彼此進(jìn)行堆疊。美光公司及其合作伙伴英特爾則掌握著32層3D NAND。西部數(shù)據(jù)/SanDisk與東芝則同SK海力士一樣,都擁有著48層芯片樣品。

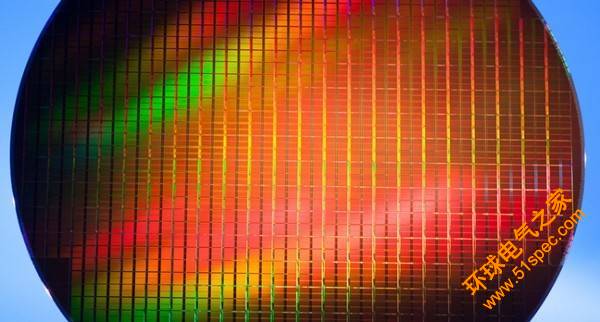

3D代工流程不僅涉及對(duì)2D NAND的水平層疊,同時(shí)還需要蝕刻數(shù)據(jù)通孔--即各層間的垂直傳輸通道--而這又是另一項(xiàng)挑戰(zhàn)。一旦層數(shù)超過(guò)64層,現(xiàn)有蝕刻設(shè)備將很難保質(zhì)保量地完成通道加工任務(wù)。

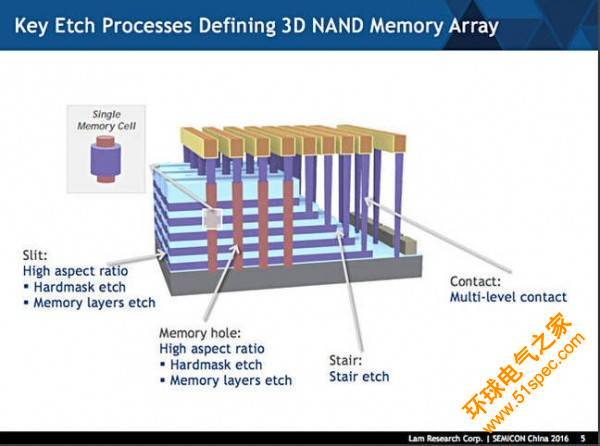

3D芯片以基片為設(shè)計(jì)起點(diǎn),在此之上使用汽相淀積工藝任選沉積的化合物作為NAND單元組件。這些沉積層形成字線(xiàn),后者接入單元中的各行,而位線(xiàn)則在金屬層中橫向跨越以上沉積層。

位線(xiàn)與字線(xiàn)間呈九十度垂直關(guān)系,同樣接入一列或者一串單元。其中字線(xiàn)與位線(xiàn)的交叉點(diǎn)被定義為單元地址。在3D NAND晶片中,亦有多條垂直串貫穿各層,用于連接各層上的不同位線(xiàn)。一塊三星3D NAND芯片可包含最高250萬(wàn)個(gè)這樣的通道,其制造難度可想而知。

在該層沉積完成后,掩模即被放置在其上,而后是進(jìn)行通孔蝕刻。接下來(lái),繼續(xù)利用蝕刻工藝在各底層與基片之間切割信道。多余的材料被移除,這樣通孔即制作完成。各通孔必須實(shí)現(xiàn)精確定位且尺寸要求均勻,通孔絕不可扭曲、粗細(xì)不均或者開(kāi)過(guò)頭,否則會(huì)破壞芯片本身。

由Lam Research發(fā)布的3D NAND蝕刻工藝示意圖。

在長(zhǎng)寬比方面(即垂直高度與通道寬度間的比值),當(dāng)前蝕刻技術(shù)可達(dá)到30:1到40:1之間,適用于32層與48層芯片設(shè)計(jì)。而即將推出的64層芯片則需要將這一比值調(diào)整至60:1到70:1之間,這意味著對(duì)應(yīng)的制程工藝還不存在。

展望未來(lái),3D NAND還將迎來(lái)96層乃至128層結(jié)構(gòu),其將需要更為夸張的長(zhǎng)寬比水平--可能在110:1到120:1之間。

NAND代工方需要等待相關(guān)蝕刻機(jī)技術(shù)的開(kāi)發(fā),或者直接堆疊現(xiàn)有3D晶片實(shí)現(xiàn)容量提升,例如將兩塊64層晶片疊加為128層,或者將兩塊48層晶片疊加為96層。兩塊晶片之間依靠一個(gè)金屬層與位串連接線(xiàn)進(jìn)行對(duì)接,從而實(shí)現(xiàn)所謂“串堆疊”機(jī)制。從理論層面講,大家也可以將更多3D晶片進(jìn)行堆疊。

這是一種潛在的可行方式,意味著我們有機(jī)會(huì)迎來(lái)64層、96層以及128層3D NAND芯片,從而繼續(xù)保證3D NAND芯片擁有理想的存儲(chǔ)容量增長(zhǎng)速度。